### **CMOS RF Power Amplifiers for Wireless Communications**

### Jonas Fritzin

# Linköpings universitet

Department of Electrical Engineering Linköpings universitet, SE-581 83 Linköping, Sweden Linköping 2011

> ISBN 978-91-7393-059-8 ISSN 0345-7524

### **CMOS RF Power Amplifiers for Wireless Communications**

Jonas Fritzin

Copyright © Jonas Fritzin, 2011 ISBN: 978-91-7393-059-8

Linköping Studies in Science and Technology Dissertations, No. 1399

ISSN: 0345-7524

Electronic Devices

Department of Electrical Engineering

Linköping University

SE-581 83 Linköping

Sweden

#### Cover image:

The cover image demonstrates the idea of outphasing.

Printed by LiU-Tryck, Linköping University Linköping, Sweden, 2011

### **Abstract**

The wireless market has experienced a remarkable development and growth since the introduction of the first modern mobile phone systems, with a steady increase in the number of subscribers, new application areas, and higher data rates. As mobile phones and wireless connectivity have become consumer mass markets, the prime goal of the IC manufacturers is to provide low-cost solutions.

The power amplifier (PA) is a key building block in all RF transmitters. To lower the costs and allow full integration of a complete radio System-on-Chip (SoC), it is desirable to integrate the entire transceiver and the PA in a single CMOS chip. While digital circuits benefit from the technology scaling, it is becoming harder to meet the stringent requirements on linearity, output power, bandwidth, and efficiency at lower supply voltages in traditional PA architectures. This has recently triggered extensive studies to investigate the impact of different efficiency enhancement and linearization techniques, like polar modulation and outphasing, in nanometer CMOS technologies.

This thesis addresses the potential of integrating linear and power-efficient PAs in nanometer CMOS technologies at GHz frequencies. In total eight amplifiers have been designed - two linear Class-A PAs, two switched Class-E PAs, and four Class-D PAs linearized in outphasing configurations. Based on the outphasing PAs, amplifier models and predistorters have been developed and evaluated for uplink (terminal) and downlink (base station) signals.

The two linear Class-A PAs with LC-based and transformer-based input and interstage matching networks were designed in a 65nm CMOS technology for 2.4GHz 802.11n WLAN. For a 72.2Mbit/s 64-QAM 802.11n OFDM signal with PAPR of 9.1dB, both PAs fulfilled the toughest EVM requirement in the standard at average output power levels of +9.4dBm and +11.6dBm, respectively. The two PAs were among the first PAs implemented in a 65nm CMOS technology.

The two Class-E PAs, intended for DECT and Bluetooth, were designed in 130nm CMOS and operated at low 'digital' supply voltages. The PAs delivered +26.4 and +22.7dBm at 1.5V and 1.0V supply voltages with PAE of 30% and 36%, respectively. The Bluetooth PA was based on thin oxide devices and the performance degradation over time for a high level of oxide stress was evaluated.

The four Class-D outphasing PAs were designed in 65nm, 90nm, and 130nm CMOS technologies. The first outphasing design was based on a Class-D stage utilizing a cascode configuration, driven by an AC-coupled low-voltage driver, to allow a 5.5V supply voltage in a 65nm CMOS technology without excessive device voltage stress. Two on-chip transformers combined the outputs of four Class-D stages. At 1.95GHz the PA delivered +29.7dBm with a PAE of 26.6%. The 3dB bandwidth was 1.6GHz, representing state-of-the-art bandwidth for CMOS Class-D RF PAs. After one week of continuous operation, no performance degradation was noticed. The second design was based on the same Class-D stage, but combined eight amplifier stages by four on-chip transformers in 130nm CMOS to achieve a state-of-the-art output power of +32dBm for CMOS Class-D RF PAs. Both designs met the ACLR and modulation requirements without predistortion when amplifying uplink WCDMA and 20MHz LTE signals.

The third outphasing design was based on two low-power Class-D stages in 90nm CMOS featuring a harmonic suppression technique, cancelling the third harmonic in the output spectrum which also improves drain efficiency. The proposed Class-D stage creates a voltage level of  $V_{\rm DD}/2$  from a single supply voltage to shape the drain voltage, uses only digital circuits and eliminates the short-circuit current present in inverter-based Class-D stages. A single Class-D stage delivered +5.1dBm at 1.2V supply voltage with a drain efficiency and PAE of 73% and 59%, respectively. Two Class-D stages were connected to a PCB transformer to create an outphasing amplifier, which was linear enough to amplify EDGE and WCDMA signals without the need for predistortion.

The fourth outphasing design was based on two Class-D stages connected to an onchip transformer with peak power of +10dBm. It was used in the development of a behavioral model structure and model-based phase-only predistortion method suitable for outphasing amplifiers to compensate for both amplitude and phase mismatches. In measurements for EDGE and WCDMA signals, the predistorter improved the margin to the limits of the spectral mask and the ACLR by more than 12dB. Based on a similar approach, an amplifier model and predistortion method were developed and evaluated for the +32dBm Class-D PA design using a downlink WCDMA signal, where the ACLR was improved by 13.5dB. A least-squares phase predistortion method was developed and evaluated for the +30dBm Class-D PA design using WCDMA and LTE uplink signals, where the ACLR was improved by approximately 10dB.

### Populärvetenskaplig sammanfattning

Trådlös kommunikation har sedan de första moderna mobiltelefonsystemen introducerades upplevt en enastående utveckling med ett ständigt ökande antal abonnenter, nya användningsområden och högre datahastigheter. Då mobiltelefoner och trådlösa apparater med radiokommunikation har blivit en massmarknad för konsumenter är det ytterst viktigt för tillverkare att ta fram små och billiga lösningar.

Effektförstärkaren är ett mycket viktigt byggblock i alla radiosändare. Effektförstärkaren sitter innan antennen och ser till att signalen blir tillräckligt stark för att sändas allt från ett tiotal meter, t.ex. Bluetooth, till tiotals kilometer, t.ex. GSM. För att minska kostnaden och nå målet med en full integrering av en komplett radio på ett chip (System-on-Chip, SoC) är det önskvärt att integrera hela kombinationen av sändare och mottagare, sändtagaren (transceiver på engelska), tillsammans med effektförstärkaren på samma CMOS-chip.

Medan digitala kretsar drar fördel av miniatyriseringen av transistorerna i CMOS blir det allt svårare att nå de tuffa kraven på linjäritet, uteffekt, bandbredd och energieffektivitet i effektförstärkaren då allt lägre spänningar används för att inte skada transistorerna. För att öka datahastigheten i trådlös kommunikation används numer både amplitud- och fasmodulering, vilket leder till dålig energieffektivitet med traditionella förstärkararkitekturer. Detta har lett till att man intresserat sig för att utvärdera nya kretstekniker och designmetoder för att kunna nå den önskade prestandan i effektförstärkare implementerade i CMOS.

Den här avhandlingen utvärderar potentialen i att integrera linjära och högeffektiva effektförstärkare och effektförstärkar-arkitekturer i CMOS-teknologier vid GHz-frekvenser. Totalt sett har åtta förstärkare konstruerats och utvärderats - varav två är linjära klass-A-förstärkare, två switchade klass-E-förstärkare samt fyra klass-D-förstärkare med konstant amplitud på utsignalen. Klass-D-förstärkarna har linjäriserats

genom outphasing-tekniken där två fasmodulerade signaler med konstant amplitud förstärks av två högeffektiva förstärkare, vars utsignaler läggs ihop för att skapa en amplitud-modulerad signal. Förutom förstärkarna, som byggts i 65nm, 90nm och 130nm CMOS-teknologier, har korrigeringsmetoder utvecklats och utvärderats för signaler för både mobiltelefoner och basstationer.

### **Preface**

This Ph.D. thesis presents my research during the period February 2007 through October 2011 at the Electronic Devices group, Department of Electrical Engineering, Linköping University, Sweden. The following papers are included in the thesis:

- Paper 1 Jonas Fritzin, Atila Alvandpour, "A 3.3V 72.2Mbit/s 802.11n WLAN Transformer-Based Power Amplifier in 65nm CMOS," *Journal of Analog Integrated Circuits and Signal Processing (Springer)*, vol. 64, no. 3, pp. 241-247, August 2010.

- Paper 2 Jonas Fritzin, Ted Johansson, Atila Alvandpour, "Impedance Matching Techniques in 65nm CMOS Power Amplifiers for 2.4GHz 802.11n WLAN," *IEEE European Microwave Conference (EuMC)*, pp. 1207-1210, Amsterdam, The Netherlands, October 2008.

- Paper 3 Jonas Fritzin, Atila Alvandpour, "Low Voltage Class-E Power Amplifiers for DECT and Bluetooth in 130nm CMOS," *IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF)*, pp. 57-60, San Diego, CA, USA, January 2009.

- Paper 4 Jonas Fritzin, Timmy Sundström, Ted Johansson, Atila Alvandpour, "Reliability Study of a Low-Voltage Class-E Power Amplifier in 130nm CMOS," *IEEE International Symposium on Circuits and Systems* (*ISCAS*), pp. 1907-1910, Paris, France, May 2010.

- Paper 5 Jonas Fritzin, Christer Svensson, Atila Alvandpour, "A Wideband Fully Integrated +30dBm Class-D Outphasing RF PA in 65nm CMOS," to be presented at IEEE International Symposium on Integrated Circuits (ISIC), Singapore, December 2011. Chip Design Competition Finalist.

- Paper 6 Jonas Fritzin, Christer Svensson, Atila Alvandpour, "A +32dBm 1.85GHz Class-D Outphasing RF PA in 130nm for WCDMA/LTE," *IEEE European Solid-State Circuits Conference (ESSCIRC)*, pp. 127-130, Helsinki, Finland, September 2011.

- Paper 7 Jonas Fritzin, Christer Svensson, Atila Alvandpour, "A Class-D Outphasing RF Amplifier with Harmonic Suppression in 90nm CMOS," *IEEE European Solid-State Circuits Conference (ESSCIRC)*, pp. 310-313, Seville, Spain, September 2010.

- Paper 8 Jonas Fritzin, Ylva Jung, Per Niklas Landin, Peter Händel, Martin Enqvist, Atila Alvandpour, "Phase Predistortion of a Class-D Outphasing RF Amplifier in 90nm CMOS," *IEEE Transactions on Circuits and Systems–II: Express Briefs*, vol. 58, no. 10, pp. 642-646, October 2011.

- Paper 9 Jonas Fritzin, Christer Svensson, Atila Alvandpour, "Design and Analysis of a Class-D Stage with Harmonic Suppression," accepted for publication in IEEE Transactions on Circuits and Systems-I: Regular Papers, 2011.

- Paper 10 Per Niklas Landin, Jonas Fritzin, Wendy Van Moer, Magnus Isaksson, Atila Alvandpour, "Modeling and Digital Predistortion of Class-D Outphasing RF Power Amplifiers," *submitted for publication*, 2011.

- Paper 11 Ylva Jung, Jonas Fritzin, Martin Enqvist, Atila Alvandpour, "Least-Squares Phase Predistortion of a +30dBm Class-D Outphasing RF PA in 65nm CMOS," *submitted for publication*, 2011.

My research has also included involvement in projects that has generated the following papers falling outside the scope of this thesis:

• Jonas Fritzin, Ted Johansson, Atila Alvandpour, "Power Amplifiers for WLAN in 65nm CMOS," *Swedish System-on-Chip Conference (SSoCC)*, Södertuna Slott, Sweden, May 2008. *Best Student Presentation Award*.

- Jonas Fritzin, Ted Johansson, Atila Alvandpour, "A 72.2Mbit/s LC-Based Power Amplifier in 65nm CMOS for 2.4GHz 802.11n WLAN," *IEEE Mixed Design of Integrated Circuits and Systems (MIXDES) Conference*, pp. 155-158, Poznan, Poland, June 2008.

- **Jonas Fritzin**, Atila Alvandpour, "A 72.2Mbit/s Transformer-Based Power Amplifier in 65nm CMOS for 2.4GHz 802.11n WLAN," *IEEE NORCHIP Conference*, pp. 53-56, Tallinn, Estonia, November 2008.

- Jonas Fritzin, Atila Alvandpour, "Low-Voltage High-Efficiency Class-E Power Amplifiers in 130nm CMOS for Short-Range Wireless Communications," *Swedish System-on-Chip Conference (SSoCC)*, Arild, Sweden, May 2009.

- Sher Azam, Rolf Jonsson, **Jonas Fritzin**, Atila Alvandpour, Qamar Wahab, "High Power, Single Stage SiGaN HEMT Class E Power Amplifier at GHz Frequencies," *IEEE International Bhurban Conference on Applied Sciences & Technology (IBCAST) Conference*, Islamabad, Pakistan, January 2010.

- Hashim Raza Khan, Qamar Ul Wahab, Jonas Fritzin, Atila Alvandpour, "A 900MHz 26.8dBm Differential Class-E CMOS Power Amplifier," *IEEE German Microwave Conference (GeMIC)*, pp. 276-269, Berlin, Germany, March 2010.

- **Jonas Fritzin**, Christer Svensson, Atila Alvandpour, "A Digital Linear CMOS RF Amplifier," *Swedish System-on-Chip Conference (SSoCC)*, Kolmården, Sweden, May 2010.

- Ted Johansson, Noora Solati, Jonas Fritzin, "A High-Linearity SiGe RF Power Amplifier for 3G and 4G Small Basestations," submitted for publication, 2011.

- **Jonas Fritzin**, Christer Svensson, Atila Alvandpour, "A Fully Integrated High Power CMOS Power Amplifier," *Swedish System-on-Chip Conference* (*SSoCC*), Varberg, Sweden, May 2011.

- Rashad Ramzan, Jonas Fritzin, Jerzy Dabrowski, Christer Svensson, "Wideband Low Reflection Transmission Line for Bare Chip on Multilayer PCB," ETRI (Electronic and Telecommunication Research Institute) Journal, vol. 33, no. 3, pp. 335-343, June 2011.

• **Jonas Fritzin**, Behzad Mesgarzadeh, Atila Alvandpour, "A Class-D Stage with Third Harmonic Suppression and DLL-Based Phase Generation," *submitted for publication*, 2011.

### **Contributions**

The main contributions of this dissertation are as follows:

- Design and implementation of two linear WLAN PAs with LC-based and transformer-based input and interstage matching networks in 65nm CMOS.

- Design and implementation of two low-voltage Class-E RF PA designs in 130nm CMOS, also evaluated from a reliability perspective.

- Design and implementation of a high-voltage Class-D stage used in two fully integrated PA designs in 65nm and 130nm CMOS with output powers larger than +30dBm and with large bandwidths.

- Design, analysis, and implementation of a Class-D stage with 3rd harmonic suppression, short-circuit current elimination, and improvement in drain efficiency.

- Development of Class-D outphasing amplifier behavioral models and predistorters, verified and evaluated in measurements on a low-power outphasing RF amplifier with on-chip transformer in 90nm CMOS and a fully integrated +32dBm PA.

- Development of a phase predistortion method with a least-squares parameter estimator suitable for outphasing PAs. The predistortion method was evaluated on a +30dBm Class-D RF PA.

### **Abbreviations**

ACLR Adjacent Channel Leakage Ratio

ACPR Adjacent Channel Power Ratio

BJT Bipolar Junction Transistor

CMOS Complementary Metal-Oxide-Semiconductor

CF Crest Factor

DC Direct Current

DE Drain Efficiency

DECT Digital Enhanced Cordless Telecommunications

EDGE Enhanced Data Rates for GSM Evolution

EVM Error Vector Magnitude FET Field-Effect Transistor

GaAs Gallium Arsenide GaN Gallium Nitride

GSM Global System for Mobile communications

HBT Heterojunction Bipolar Transistor

IC Integrated Circuit

InP Indium Phosphide

IEEE The Institute of Electrical and Electronics Engineers

ITRS International Technology Roadmap for Semiconductors

LO Local Oscillator

LTE Long Term Evolution

MMIC Monolithic Microwave Integrated Circuit

MESFET Metal-Semiconductor Field Effect Transistor

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

NMOS N-channel Metal-Oxide-Semiconductor

PA Power Amplifier

PAE Power-Added Efficiency

PAPR Peak-to-Average Power Ratio

PCB Printed Circuit Board

PMOS P-channel Metal-Oxide-Semiconductor

PAE Power-Added Efficiency

RF Radio Frequency

RMS Root-Mean-Square

WLAN Wireless Local Area Network

WCDMA Wideband Code Division Multiple Access

### Acknowledgments

Without the help, support, and encouragement of a large number of people it would not be possible for me to write this thesis. I would like want to thank the following people and organizations:

- My supervisor and advisor Professor Atila Alvandpour, for your guidance, patience, and support. Thanks for giving me the opportunity to pursue a career as Ph.D. student.

- Professor emeritus Christer Svensson for interesting discussions, giving valuable comments and sharing his experience.

- Dr. Timmy Sundström for excellent collaboration during student labs, graduate courses, and for being a great friend.

- Adj. Prof. Ted Johansson for always being ready to review a paper at any

day of the week and at any time of the day. I also appreciate all our

discussions regarding power amplifier design and for proofreading this

thesis and contributing with many suggestions on improvements.

- I want to thank Dr. Martin "Word" Hansson for being an excellent colleague and friend and providing the Word template for this thesis.

- Dr. Henrik Fredriksson deserves a great deal of thanks for all help and useful discussions about all kinds of stuff and for proofreading this thesis and contributing with several suggestions on improvements.

- Infineon Technologies Nordic AB, Sweden, and Infineon Technologies AG, Germany, deserves a great deal of thanks for sponsoring the chip tapeouts in their CMOS technologies. Intel Corporation, USA, and Ericsson Research, Sweden, are acknowledged for sponsoring the research projects.

- All the past and present members of the Electronic Devices research group, especially Ass. Prof. Jerzy Dabrowski, Adj. Prof. Aziz Ouacha, Asst. Prof.

Behzad Mesgarzadeh, Dr. Håkan Bengtson, Dr. Christer Jansson, Dr. Mostafa Osgooei, Dr. Rashad Ramzan, Dr. Naveed Ahsan, Dr. Shakeel Ahmad, M.Sc. Ali Fazli, M.Sc. Dai Zhang, M.Sc. Amin Ojani, M.Sc. Fahad Qazi, M.Sc. Omid Najari, M.Sc. Ameya Bhide, M.Sc. Daniel Svärd, and M.Sc. Duong Quoc Tai. Thanks for creating such a great research environment.

- M.Sc. Ylva Jung and Ass. Prof. Martin Enqvist, Automatic Control group at Linköping University, and M.Sc. Per Landin, Gävle University, and Prof. Peter Händel, Kungliga Tekniska Högskolan, Stockholm, for the collaboration on predistortion methods for power amplifiers.

- Our secretaries Jenny Stendahl and Anna Folkeson for taking care of all administrative issues. Arta Alvandpour, Thomas Johansson, and Greger Karlström, for solving all computer related issues.

- I greatly appreciate the generous support from Rohde & Schwarz, Stockholm, to easily borrow equipment and the assistance of Henrik Karlström, Johan Brobäck, Anders Sundberg, and Pontus Segerberg. I also would like to thank Ronny Peschel and Thomas Göransson at Agilent Technologies, Stockholm, for letting us borrow equipment whenever needed.

- Thanks to all friends and family who have encouraged me during the years, but who I could not fit in here.

- My sweet brothers Joakim and Johan for all discussions about things not related to science and technology.

- Last, but not least, my wonderful parents Jörn and Berit Fritzin for always encouraging and supporting me in whatever I do.

Jonas Fritzin Linköping, October 2011

## **Contents**

| Abstra    | ct                                               | iii  |

|-----------|--------------------------------------------------|------|

| Populä    | rvetenskaplig sammanfattning                     | v    |

| Preface   | 3                                                | vii  |

| Contril   | butions                                          | X    |

| Abbrev    | viations                                         | xii  |

| Acknow    | wledgments                                       | XV   |

| Conten    | its                                              | xvii |

| List of   | Figures                                          | xxi  |

| Part I Ba | ckground                                         | 1    |

| Chapter 1 | Introduction                                     | 3    |

| 1.1       | Motivation and Scope of This Thesis              | 3    |

| 1.2       | Organization of This Thesis                      | 5    |

| 1.3       | Summary of Papers                                | 5    |

| 1.4       | Brief History of RF Technology, Transistors, and |      |

| Integ     | rated Circuits                                   | 7    |

| 1.5       | Future Possibilities and Challenges              | 8    |

|       | 1.6          | Semiconductor Materials                                        | 9        |

|-------|--------------|----------------------------------------------------------------|----------|

|       | 1.6          | 2 111-11-16 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                      | 9        |

|       | 1.6.<br>1.7  | 2 Comparison of Silicon and Other Semiconductors<br>References | 10<br>12 |

| Chapt | ter 2        | CMOS Device Modeling and Parasitics                            | 15       |

|       | 2.1          | Introduction                                                   | 15       |

|       | 2.2          | The MOS Device                                                 | 15       |

|       | 2.2          | 1 Structure                                                    | 15       |

|       | 2.2.         |                                                                | 16       |

|       | 2.2.<br>2.2  |                                                                | 17<br>19 |

|       | 2.3          |                                                                | 21       |

|       |              |                                                                |          |

| Chapt | ter 3        | The RF Power Amplifier                                         | 25       |

|       | 3.1          | Introduction                                                   | 25       |

|       | 3.2          | Power Amplifier Fundamentals                                   | 25       |

|       | 3.2          | 1                                                              | 26       |

|       | 3.2          | 3                                                              | 27       |

|       | 3.2.<br>Rat  |                                                                | ver      |

|       | 3.2          |                                                                | 28       |

|       | 3.2          |                                                                | 29       |

|       | 3.3          | Power Amplifier Classes                                        | 32       |

|       | 3.3          |                                                                | 32       |

|       | 3.3.         |                                                                | 34       |

|       | 3.3.<br>3.3. |                                                                | 35<br>35 |

|       | 3.3          |                                                                | 37       |

|       | 3.3          |                                                                | 41       |

|       | 3.4          | References                                                     | 42       |

| Chapt | ter 4        | Matching Techniques                                            | 47       |

|       | 4.1          | Introduction                                                   | 47       |

|       | 4.2          | Conjugate and Power Match                                      | 47       |

|       | 4.3          | Load-pull                                                      | 48       |

|       | 4.4          | Matching Network Design                                        | 50       |

|       | 4.4          |                                                                | 50       |

|           |                                                  | xix      |

|-----------|--------------------------------------------------|----------|

| -         | .4.2 Balun                                       | 53       |

| 4.5       |                                                  | 55       |

|           | .5.1 LC-Based Matching Network                   | 55       |

|           | .5.2 Transformer-Based Matching Network          | 57       |

| 4.6       | .5.3 Cascode Stage<br>References                 | 60<br>60 |

|           |                                                  |          |

| -         | 5 Linearization and Efficiency Enhancement       |          |

| 1 ecnniqu | es for Power Amplifiers                          | 65       |

| 5.1       | Introduction                                     | 65       |

| 5.2       | Polar Modulation                                 | 66       |

| 5.3       | Outphasing                                       | 66       |

| 5         | .3.1 Outphasing Background                       | 66       |

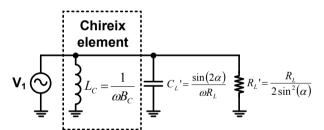

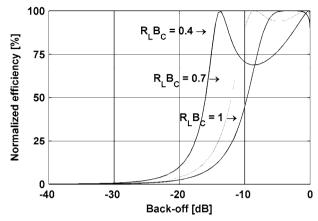

| 5         | .3.2 Chireix Combiner and Comparison of PA Types | 68       |

| 5.4       | Comparison of State-of-the-Art PAs               | 71       |

| 5.5       | Predistortion of Class-D Outphasing Amplifiers   | 75       |

| 5.6       | References                                       | 76       |

| Chapter ( | 6 CMOS Device Reliability                        | 83       |

| 6.1       | Introduction                                     | 83       |

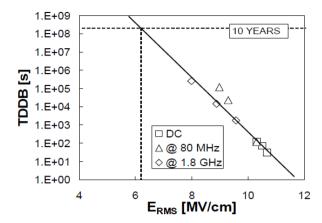

| 6         | .1.1 Gate oxide breakdown                        | 84       |

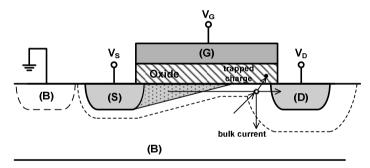

|           | .1.2 Hot carrier degradation                     | 85       |

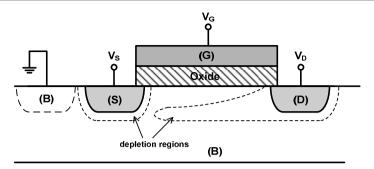

|           | 1.3 Punch-trough and drain-bulk breakdown        | 86       |

|           | .1.4 Required time of operation References       | 86<br>87 |

| 6.2       | References                                       | 8/       |

| Chapter 7 | 7 Conclusions and Future Work                    | 91       |

| 7.1       | Summary                                          | 91       |

| 7.2       | Conclusions and Future Work                      | 92       |

| 7.3       | References                                       | 93       |

| Part II I | Papers                                           | 95       |

| Chapter 8 | 3 Paper 1                                        | 97       |

| Chapter 9 | Paper 2                                          | 107      |

| 1         |                                                  | -        |

| 113 |

|-----|

| 119 |

| 125 |

| 131 |

| 137 |

| 143 |

| 151 |

| 163 |

| 173 |

|     |

# **List of Figures**

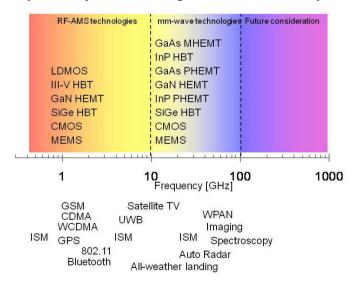

| Figure 1.1: Application spectrum and semiconductors likely to be used today [19]                     | 9    |

|------------------------------------------------------------------------------------------------------|------|

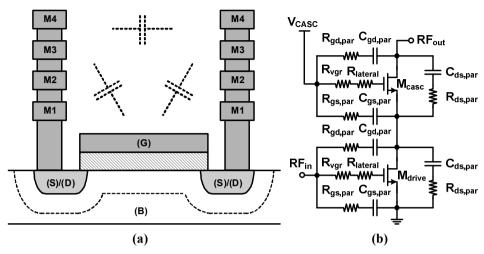

| Figure 2.1: Schematic and cross section view of an NMOS transistor                                   | . 16 |

| Figure 2.2: (a) Intrinsic small-signal model of MOS transistor [1] (b) Small-signal                  |      |

| model with extrinsic elements added                                                                  | . 18 |

| Figure 2.3: Extrinsic capacitances in the MOS transistor                                             | . 18 |

| Figure 2.4: (a) Parasitic capacitances between gate, drain, and source (b) Model of                  |      |

| cascode stage with parasitics, incl. the vertical gate resistance                                    | . 19 |

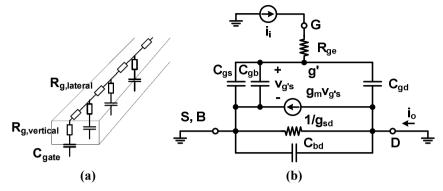

| Figure 2.5: (a) Vertical gate resistance (b) Circuit to estimate $\omega_T$                          |      |

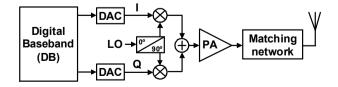

| Figure 3.1: Block diagram of a direct-conversion transmitter                                         | . 25 |

| Figure 3.2: Power amplifier (PA) with two driver stages, A1 and A2, connected to an                  |      |

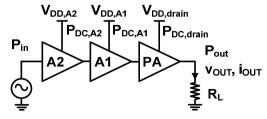

| antenna                                                                                              | . 26 |

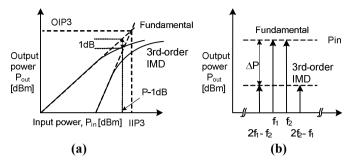

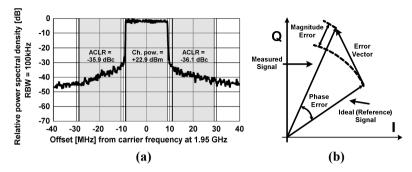

| Figure 3.3: (a) Gain compression curve (b) Intermodulation spectrum of two-tone tes                  | t30  |

| Figure 3.4: (a) ACLR measurement for an LTE signal [13] (b) Vector definitions in                    |      |

| EVM                                                                                                  | . 31 |

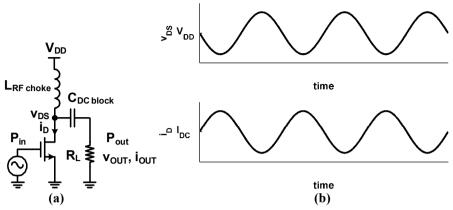

| Figure 3.5: (a) Generic single-stage Class-A/B/C power amplifier (b) Drain voltage a                 | nd   |

| current waveforms in an ideal Class-A                                                                |      |

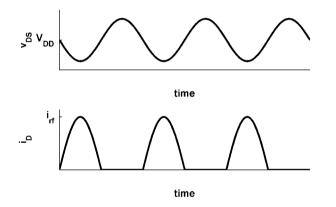

| Figure 3.6: Drain voltage and current waveforms in an ideal Class-B                                  |      |

| Figure 3.7: (a) Class-D amplifier (b) Schematic of CMOS inverter including dynamic                   |      |

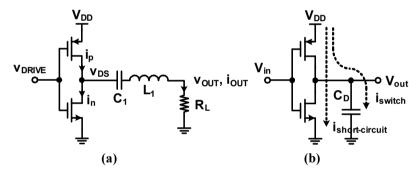

| currents                                                                                             | . 36 |

| Figure 3.8: Class-D amplifier waveforms                                                              | . 36 |

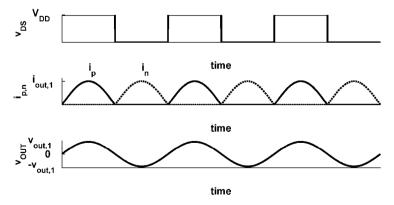

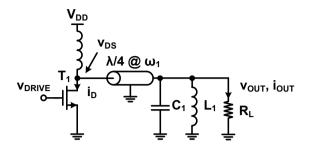

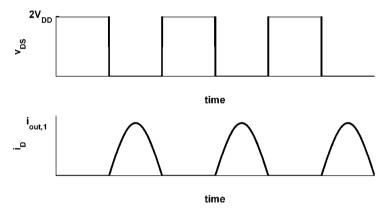

| Figure 3.9: Class-E amplifier                                                                        | . 38 |

| Figure 3.10: Normalized drain voltage and current waveforms in an ideal Class-E [2]                  | 81   |

|                                                                                                      | . 38 |

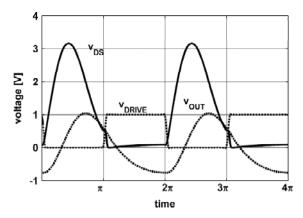

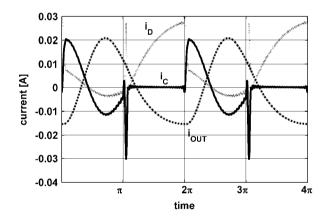

| Figure 3.11: Simulation results of drain voltage, $v_{DS}$ , driver signal, $v_{DRIVE}$ , and output | ī    |

| voltage, $v_{OUT}$                                                                                   | . 39 |

|                                                                                                      |      |

| Figure 3.12: Simulation current waveforms: drain current, $i_D$ , current through shunt                                                                               |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| capacitance, $i_C$ , output current, $i_{OUT}$                                                                                                                        | 39   |

| Figure 3.13: Class-F amplifier                                                                                                                                        |      |

| Figure 3.14: Class-F amplifier waveforms                                                                                                                              | 42   |

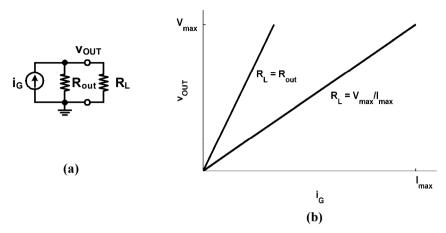

| Figure 4.1: (a) Current generator with output resistance, $R_{out}$ , and load, $R_L$ , (b)                                                                           |      |

| Conjugate match, $R_L = R_{out}$ , and loadline match, $R_L = V_{\text{max}}/I_{\text{max}}$ ; $R_{out} >> R_L$                                                       | 48   |

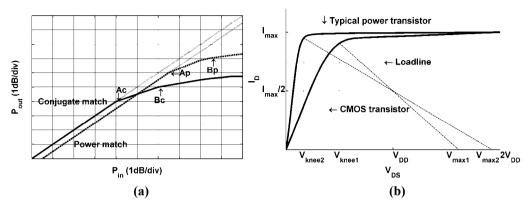

| Figure 4.2: (a) Compression characteristics for conjugate (c) and power match (p) w markers at maximum linear points (Ac, Ap), and at the 1dB compression points (Bc, | ith  |

| Bp)                                                                                                                                                                   | 49   |

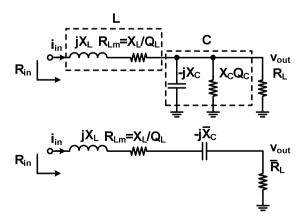

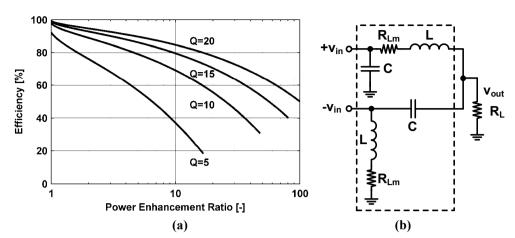

| Figure 4.3: L-matching network                                                                                                                                        | 50   |

| Figure 4.4: (a) Efficiency [9] of L-matching network for inductor quality factor, $Q_L$                                                                               |      |

| Q, and Power Enhancement Ratio, $E$ (b) Lattice-type balun inside the box with dash                                                                                   | ied  |

| lines driven by a differential signal, $+v_{in}$ and $-v_{in}$                                                                                                        | 52   |

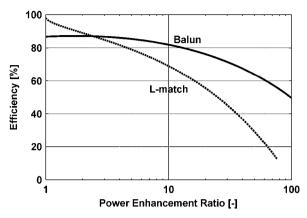

| Figure 4.5: Efficiency of L-match and balun for $Q_L = 10$                                                                                                            | 53   |

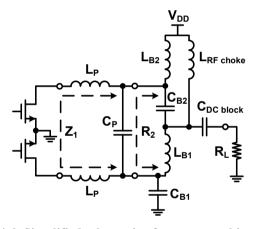

| Figure 4.6: Simplified schematic of output matching network, where PCB transmiss                                                                                      | sion |

| lines are omitted                                                                                                                                                     | 53   |

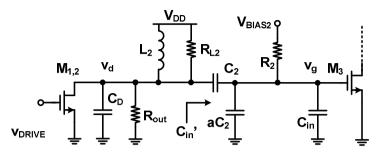

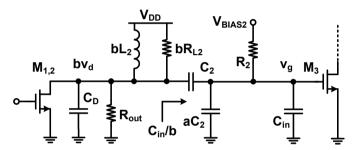

| Figure 4.7: Power amplifier with LC-based matching networks in Paper 2 [11]                                                                                           | 55   |

| Figure 4.8: Interstage matching between first and second stage                                                                                                        | 56   |

| Figure 4.9: Capacitive division                                                                                                                                       | 56   |

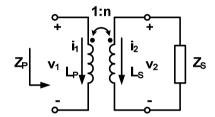

| Figure 4.10: Ideal transformer [12]                                                                                                                                   | 57   |

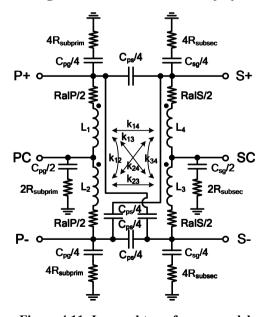

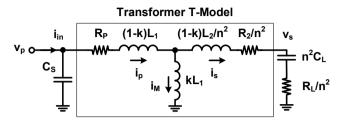

| Figure 4.11: Lumped transformer model                                                                                                                                 | 57   |

| Figure 4.12: Transformer T-model                                                                                                                                      | 59   |

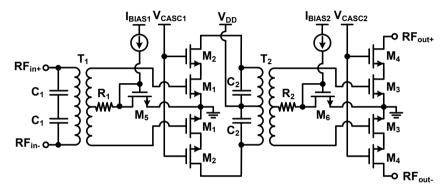

| Figure 4.13: Power amplifier with transformer-based input and interstage matching                                                                                     |      |

| networks in Paper 1 [18]                                                                                                                                              | 59   |

| Figure 5.1: Polar Modulation                                                                                                                                          | 66   |

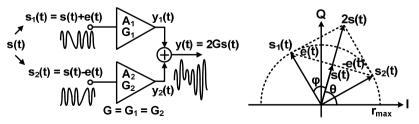

| Figure 5.2: Outphasing                                                                                                                                                |      |

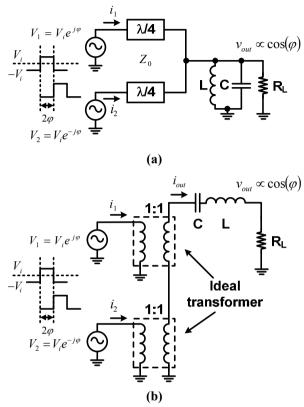

| Figure 5.3: (a) Transmission line combiner [12] (b) Transformer combiner [12]                                                                                         | 68   |

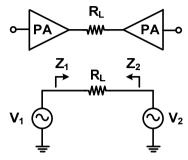

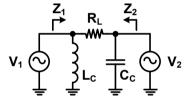

| Figure 5.4: Combining with no isolation                                                                                                                               |      |

| Figure 5.5: Combining with Chireix compensation elements                                                                                                              |      |

| Figure 5.6: Load impedance compensation for $V_1$ [9]                                                                                                                 | 69   |

| Figure 5.7: Efficiency at power back-off with Chireix compensation elements                                                                                           | 70   |

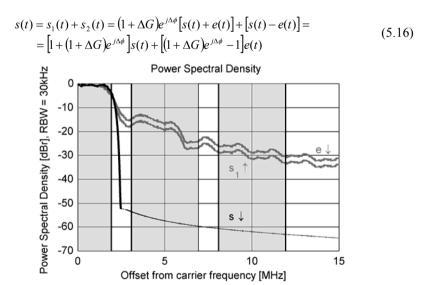

| Figure 5.8: Power spectral density of $s(t)$ , $s_1(t)$ , and $e(t)$ for an uplink WCDMA sign                                                                         | nal  |

|                                                                                                                                                                       | 75   |

| Figure 6.1: Time-Dependent Dielectric Breakdown (TDDB) plotted versus oxide rm                                                                                        | S    |

| field value measured at DC, 80MHz and 1.8GHz [14]                                                                                                                     |      |

| Figure 6.2: Class-D stage proposed in Paper 5 [15] and Paper 6 [16]                                                                                                   | 85   |

| Figure 6.3: Hot carrier stress                                                                                                                                        |      |

| Figure 6.4: Punch-through                                                                                                                                             | 87   |

# Part I Background

### Chapter 1

### Introduction

### 1.1 Motivation and Scope of This Thesis

The wireless market has experienced a remarkable development and growth since the introduction of the first modern mobile phone systems, with a steady increase in the number of subscribers, new application areas, and higher data rates. As mobile phones and integration of wireless connectivity have become consumer mass markets, the prime goal of the IC manufacturers is to provide low-cost solutions.

CMOS has for a long time been the choice for digital integrated circuits due to its high level of integration, low-cost, and constant enhancements in performance. The RF circuits have typically been predominantly designed in GaAs [1] and silicon bipolar, due to the better performance at radio frequencies. However, due to the significant scaling of the MOS transistors, the transition frequency has reached over 100GHz. Along with the enhancements in speed, the MOS transistors have become popular to use for RF applications. The digital baseband circuits have successfully been integrated in CMOS, as well as most radio building blocks, and the last part to be efficiently integrated in CMOS is the Power Amplifier (PA). To lower the cost and to achieve full integration of a radio System-on-Chip (SoC), it is desirable to integrate the entire transceiver and the PA in a single CMOS chip. Since the PA often is the most power hungry component in the transmitter, it is important to minimize the power consumption to achieve a highly power-efficient and to extend battery life-time of portable devices. With a high efficiency, the heat dissipation of the devices is reduced, lowering the requirements and cost of the packaging of the IC.

While digital circuits benefit from the technology scaling, it is becoming harder to meet the stringent requirements on linearity, output power, bandwidth, and efficiency at lower supply voltages in traditional PA architectures. This has recently triggered extensive studies to investigate the impact of different efficiency enhancement and linearization techniques, like polar modulation and outphasing, in nanometer CMOS technologies.

This thesis addresses the potential of integrating linear and power-efficient PAs in nanometer CMOS technologies at GHz frequencies. In total eight amplifiers have been designed - two linear Class-A PAs, two switched Class-E PAs, and four Class-D PAs linearized in outphasing configurations. Based on the outphasing PAs, amplifier models and predistorters have been developed and evaluated for uplink (terminal) and downlink (base station) signals.

### 1.2 Organization of This Thesis

This thesis is organized into two parts:

- Part I Background

- Part II Papers

Part I provides the background for the concepts used in the papers.

Chapter 1 discusses the background of RF technology, history of integrated circuits, and future challenges in RF CMOS circuit design with emphasis on PA design.

Chapter 2 treats the operation of the transistor and intrinsic/extrinsic parasitics.

Chapter 3 introduces concepts and definitions used in PAs and describe the fundamental operation of the amplifier classes used in the papers.

Chapter 4 describes the matching techniques for PAs, specifically targeting the PAs in Paper 1 and Paper 2.

Chapter 5 introduces two major linearization and efficiency enhancements techniques for switched amplifiers, i.e. polar modulation and outphasing. Class-D and outphasing RF PA implementations are presented in **Paper 5 - Paper 9**. This chapter also provides an introduction to the predistortion methods presented in **Paper 8**, **Paper 10**, and **Paper 11**.

Chapter 6 discusses the major breakdown mechanisms of MOS devices from a circuit designer's perspective. This chapter serves as a background for the PA implementations in **Paper 3 - Paper 6**.

Chapter 7 concludes the thesis and suggests further areas to be investigated.

In Part II the papers included in this thesis are presented in full.

### 1.3 Summary of Papers

The two linear PAs, presented in **Paper 1** and **Paper 2**, have been designed in a 65nm CMOS technology, targeting the 2.4GHz 802.11n WLAN standard. The PAs are two-stage amplifiers with LC-based and transformer-based input and interstage matching networks, respectively. For a 72.2Mbit/s 64-QAM 802.11n OFDM signal with PAPR of 9.1dB, both PAs fulfilled the toughest EVM requirement at average output power levels of +9.4dBm and +11.6dBm, respectively. The PAs were among the first PAs implemented in a 65nm CMOS technology.

Two Class-E PAs intended for DECT and Bluetooth, presented in **Paper 3** and **Paper 4**, have been designed in 130nm CMOS and operated at low 'digital' supply voltages. At 1.5V supply voltage and 1.85GHz, the DECT PA delivered +26.4dBm of output power with a drain efficiency (DE) and power-added efficiency (PAE) of 41% and 30%, respectively. At 1.0V supply voltage and 2.45GHz, the Bluetooth PA delivered +22.7dBm of output power with a DE and PAE of 48% and 36%,

respectively. The Bluetooth PA was based on thin oxide devices and the performance degradation over time for a high level of oxide stress was evaluated.

The four Class-D outphasing PAs have been designed in 65nm, 90nm, and 130nm CMOS technologies. The first outphasing design, presented in Paper 5, was based on a Class-D stage utilizing a cascode configuration, driven by an AC-coupled low-voltage driver, to allow a 5.5V supply voltage in a 65nm CMOS technology without excessive device voltage stress. Two on-chip transformers combined the outputs of four Class-D stages. At 1.95GHz and a 5.5V supply voltage, the output power was +29.7dBm with a DE and PAE of 30.2% and 26.6%, respectively. The 3dB bandwidth was 1.6GHz (1.2-2.8GHz), representing the state-of-the-art bandwidth among published Class-D RF PAs. The PA was operated for 168 hours (1 week) without any performance degradation. The second design, presented in Paper 6, was based on the same Class-D stage as the first design, but combined eight amplifier stages by utilizing four on-chip transformers in a 130nm CMOS technology. At 1.85GHz and 5.5V supply voltage, the output power was +32dBm with a DE and PAE of 20.1% and 15.3%, respectively. The peak output power of +32dBm represents the state-of-the-art output power among published Class-D RF PAs. Both designs met the ACLR and modulation requirements without predistortion when amplifying uplink WCDMA and LTE (20MHz, 16-QAM) signals.

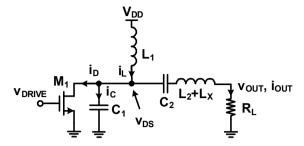

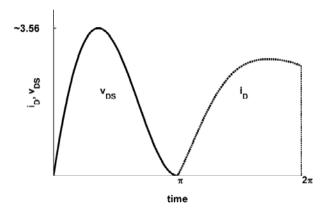

The third outphasing design was based on two low-power Class-D stages in 90nm CMOS featuring a harmonic suppression technique, presented in **Paper 7** and analysed in **Paper 9**, cancelling the third harmonic in the output spectrum which also improves drain efficiency. The proposed Class-D stage creates a voltage level of  $V_{\rm DD}/2$  from a single supply voltage to shape the drain voltage, uses only digital circuits and eliminates the short-circuit current present in inverter-based Class-D stages. A single Class-D stage delivered +5.1dBm at 1.2V supply voltage with a DE and PAE of 73% and 59%, respectively. Two Class-D stages were connected to a PCB transformer to create an outphasing amplifier, which was linear enough to amplify EDGE and WCDMA signals without the need for predistortion.

The fourth outphasing design, presented in **Paper 8**, is based on two Class-D amplifier stages connected to an on-chip transformer. The peak power of the amplifier was +10dBm and has been used in the development of a behavioral model structure and a model-based phase-only predistortion method suitable for Class-D outphasing RF amplifiers to compensate for both amplitude and phase mismatches. In measurements at 2GHz, the predistorter proved to be successful and improved the margin to the limits of the EDGE spectral mask at 400kHz and the WCDMA ACLR at 5MHz offset by 12.2-12.4dB. Based on a similar approach, presented in **Paper 10**, an amplifier model and predistortion method were developed and evaluated for the +32dBm Class-D PA design using a downlink WCDMA signal, where the ACLR at 5MHz was improved by 13.5dB. In **Paper 11**, a least-squares phase predistortion method was developed and evaluated for the +30dBm Class-D PA design using WCDMA and LTE uplink signals, where the ACLR was improved by approximately 10dB.

# 1.4 Brief History of RF Technology, Transistors, and Integrated Circuits

This chapter briefly enlightens the main milestones, which have made the electronics and wireless revolution possible. Furthermore, a comparison of semiconductor technologies and their current performance will be discussed along with their potential performance in the future.

The initial step towards solid-state devices was taken in 1874, as Ferdinand Braun discovered the metal-semiconductor contact, but it took another 51 years (1925) until the Field-Effect Transistor (FET) was patented by the physicist Julius Edgar Lilienfeld. In 1947, at Bell Labs in the US, a bipolar transistor device was developed by John Bardeen, Walter Brattain, and William Shockley, who received the Nobel Prize for their invention in 1956. The first integrated circuit (IC) was developed in 1958 by Jack Kilby, working at Texas Instruments, and consisted of a transistor, a capacitor, and resistors on a piece of germanium [2], [3]. Independent from Kilby, in the following year Robert Noyce [4] invented an IC with planar interconnections using photolithography and etching techniques still used today. However, it took another few years until Frank Wanlass in 1963, at Fairchild Semiconductor, developed the Complementary Metal-Oxide-Semiconductor (CMOS) process, which enabled the integration of both NMOS and PMOS transistors on the same chip. The first demonstration circuits were an inverter and a ring-oscillator [5].

In 1965 Gordon Moore, one of Intel's co-founders, predicted that the number of devices would double every twelve months [6]. The prediction was modified in 1975 [7], such that the future rate of increase in complexity would rather double every two years instead of every year and became known as Moore's law. In some people's opinion this prediction became a self-fulfilling prophecy that has emerged as one of the driving principles in the semiconductor industry, as engineers and researchers have been challenged to deliver annual breakthroughs to comply with the "law".

Since the '70s, the progress in several areas has made it feasible to keep up the pace in the electronics development to deliver more reliable, complex, and high-performance integrated circuits. A few years ago, Intel announced the first microprocessor with more than 2 billion transistors on the same die in a 65nm process [8], which would not have been possible without the tremendous scaling of CMOS transistors. However, with the transistor scaling, the issues with leakage become troublesome in traditional planar CMOS transistors, but have been reduced in new transistors like the three-dimensional FinFETs [9].

As mass-consumer products require a low manufacturing cost, silicon have been preferred as semiconductor material, as it has been possible to integrate more and more functionality along with a constant increase of performance. Without the scaling of both transistors and the cost of manufacturing of CMOS transistors, high-technology

products like portable computers and mobile phones would probably not have been mass-consumer markets [10].

The birth of wireless communication is dated to 1895, when Guglielmo Marconi managed to transmit a radio signal for more than a kilometer with a spark-gap transmitter, which was followed up by the first transatlantic radio transmission in 1902. The first analog mobile phone system in Scandinavia, Nordic Mobile Telephone System (NMT), appeared in the early 1980s. The NMT system was succeeded by the GSM system (Global System for Mobile communications: originally Groupe Spécial Mobile) in the '90s, which has been followed by several new standards for long and short distance communications. The evolution from the GSM system in the '90s with raw data rates of some kbps to today's high-speed WLAN and LTE standards with data rates of several 100Mbps has made it feasible to not only transmit voice data, but also transmit and receive pictures and movies. The significant increase in data rates has been viable through several enhancements, not only on the device level, but also through the development of more complex modulation schemes. They have evolved from Gaussian Minimum-Shift Keying (GMSK) modulation used in GSM to amplitude and phase modulations with large Peak-to-Average Power Ratio (PAPR) as in the WLAN and the LTE systems to support higher data rates, requiring highly linear transmitters. The radio architectures have evolved into architectures called transceivers, including both the transmitter and receiver sections. The digital baseband (DB) circuits, the local oscillator (LO), the mixer, the low-noise amplifiers (LNA) [11], the analog-to-digital converters (ADC), and the digital-to-analog converters (DAC) have successfully been implemented in CMOS and BiCMOS technologies [12]. However, one of the most challenging building blocks to efficiently integrate in CMOS is the PA. It has been predominantly designed in other technologies due to the higher efficiency [1], like GaAs HBTs [13] and Metal-Semiconductor Field Effect Transistors (MESFET) [14], Si BJT or SiGe HBT [15] for mobile handsets. One of the first CMOS RF PAs capable of delivering 1W of output power was presented in 1997 and implemented in a 0.8µm technology operating at 824-849MHz [16]. In the following year, a PA in a 0.35µm technology was presented and operated at 2GHz with an output power of 1W [17].

### 1.5 Future Possibilities and Challenges

Since the early '90s, silicon devices have had good enough performance for transceiver design [18]. By combining the low cost and integration capabilities of CMOS/BiCMOS, these technologies will make them the choice of RF transceivers with fully-integrated PAs, as long as RF and system design goals can be achieved. Figure 1.1 [19] shows an application spectrum and what semiconductors are likely to be used in certain frequency ranges. The application spectrum is currently predicted up to 100GHz, but both Indium Phosphide (InP) High Electron Mobility Transistor (HEMT) and Gallium Arsenide (GaAs) Metamorphic High Electron Mobility Transistor (MHEMT) have shown acceptable performance in the THz regime and can be expected to continuously dominate for extremely high frequency applications.

The main drivers of wireless communications systems today are cost, frequency bands, power consumption, functionality, size, volume of production, and standards. As wireless functionality has been integrated into more and more applications and entered mass-consumer markets, silicon-based technologies have continuously replaced the traditional III-V semiconductors when acceptable RF performance has been met. In PAs, the discussion will regard output power, linearity, efficiency, bandwidth, and integration. Currently, the market of WLAN transceivers is dominated by CMOS, where fully-integrated solutions, including the PA, have been presented [20]-[22]. Silicon-based technologies will be the choice for high volume and cost sensitive markets, but is not expected to be the choice when the key demands are very high gain, very high output power, and extremely low noise.

### 1.6 Semiconductor Materials

### 1.6.1 Scaling Trend of CMOS

As shown in Figure 1.1 a number of semiconductor materials exist, which are suitable for RF circuit design. Considering the scaling trend of MOS device in Table 1-1, we can foresee almost a reduction of two of the gate oxide thickness and a reduction of four of the gate length for the thin oxide devices in the next ten years [18], leading to potentially extreme  $f_T$ . To meet the high output power requirements in PAs a large supply voltage is desirable. Thus it is likely to use the thick oxide (I/O) devices or a combination of both devices in PA design. The trend for the thick oxide devices is not as extreme as for the thin oxide devices, as they are expected to have an oxide thickness of 2.6nm in ten years, comparable to existing thick oxide devices today.

Figure 1.1: Application spectrum and semiconductors likely to be used today [19]

### 1.6.2 Comparison of Silicon and Other Semiconductors

As GaAs was one of the first semiconductors used in RF design and is still used in most terminal PAs, a short comparison of the specific properties of III-V compounds and silicon is given here. Table 1-2 shows the key characteristics of the basic materials of the most common MMIC technologies.

Considering the carrier velocity and mobility, they are higher for the electrons than for the holes. The difference between electrons and holes is much larger in III-V devices (e.g. GaAs) than for silicon devices [12], but the carrier velocity and mobility of electrons are lower for silicon devices. Due to the large difference in complementary III-V devices and the lower hole carrier velocity and mobility in GaAs, silicon technologies are better suited when it comes to high speed complementary logic. However, for high-speed circuits n-based GaAs devices are advantageous as long as no complementary devices are needed.

Another important parameter when considering complementary logic is the thermal conductivity as listed in Table 1-2. If the parameter is low, it implies issues to dissipate heating. Considering the two billion-transistor processor [8], a good thermal conductivity of the substrate material is necessary in order to make sure that the chip is not overheated. The comparable integration level in GaAs is typically limited to approximately 1000 transistors [12].

A parameter not beneficial in the silicon case is the substrate resistivity, which is

| TABLE 1-1: PREDICTED ( | CMOS SCALING BY ITRS | 181 |

|------------------------|----------------------|-----|

|------------------------|----------------------|-----|

| Year of production            | 2010 | 2013 | 2016 | 2019 | 2022 |

|-------------------------------|------|------|------|------|------|

| Technology node [nm]          | 45   | 32   | 22   | 16   | 11   |

| Thin oxide device             |      |      |      |      |      |

| - Nominal V <sub>DD</sub> [V] | 1.0  | 1.0  | 0.8  | 0.8  | 0.7  |

| - t <sub>ox</sub> [nm]        | 1.5  | 1.2  | 1.1  | 1.0  | 0.8  |

| - Peak f <sub>T</sub> [GHz]   | 280  | 400  | 550  | 730  | 870  |

| - Peak f <sub>max</sub> [GHz] | 340  | 510  | 710  | 960  | 1160 |

| - Ids [μA/μm]: min L          | 8    | 6    | 4    | 3    | 2    |

| Thick oxide device            |      |      |      |      |      |

| - Nominal VDD [V]             | 1.8  | 1.8  | 1.8  | 1.5  | 1.5  |

| - t <sub>ox</sub> [nm]        | 3    | 3    | 3    | 2.6  | 2.6  |

| - Peak f <sub>T</sub> [GHz]   | 50   | 50   | 50   | 70   | 70   |

| - Peak f <sub>max</sub> [GHz] | 90   | 90   | 90   | 120  | 120  |

| Passive elements for PAs      |      |      |      |      |      |

| - Inductor Q [1GHz, 5nH]      | 14   | 18   | 18   | 18   | 18   |

| - Capacitor Q [1GHz, 10pF]    | >100 | >100 | >100 | >100 | >100 |

| - RF cap. density [fF/μm²]    | 5    | 7    | 10   | 10   | 12   |

TABLE 1-2: COMPARISON OF MMIC TECHNOLOGIES [12], [24]

|                                                         | Silicon                              | SiC                | InP                  | GaAs                 | GaN                |

|---------------------------------------------------------|--------------------------------------|--------------------|----------------------|----------------------|--------------------|

| Electron mobility at 300K [cm²/Vs]                      | 1500                                 | 700                | 5400                 | 8500                 | 1000-2000          |

| Hole mobility at 300K [cm²/Vs]                          | 450                                  | n.a                | 150                  | 400                  | n.a.               |

| Peak/saturated electron velocity [10 <sup>7</sup> cm/s] | 1.0/1.0                              | 2.0/2.0            | 2.0/2.0              | 2.1/n.a              | 2.1/1.3            |

| Peak/saturated hole velocity [10 <sup>7</sup> cm/s]     | 1.0/1.0                              | n.a                | n.a                  | n.a                  | n.a                |

| Bandgap [eV]                                            | 1.1                                  | 3.26               | 1.35                 | 1.42                 | 3.49               |

| Critical breakdown field [MV/cm]                        | 0.3                                  | 3.0                | 0.5                  | 0.4                  | 3.0                |

| Thermal conductivity [W/(cm K)]                         | 1.5                                  | 4.5                | 0.7                  | 0.5                  | >1.5               |

| Substrate resistivity [Ωcm]                             | 1-20                                 | 1-20               | >1000                | >1000                | >1000              |

| Number of transistors in IC                             | >1 billion                           | <200               | <500                 | <1000                | <50                |

| Transistors                                             | MOSFET,<br>Bipolar,<br>HBT,<br>LDMOS | MESFET,<br>HEMT    | MESFET,<br>HEMT, HBT | MESFET,<br>HEMT, HBT | MESFET,<br>HEMT    |

| Costs prototype,<br>mass fabrication                    | High,<br>low                         | Very high,<br>n.a. | High,<br>very high   | Low,<br>high         | Very high,<br>n.a. |

relatively low compared to the III-V semiconductors, and degrades the quality factor of integrated passives [23]. In Table 1-1 the predicted quality factors at 1GHz are given for on-chip inductors and capacitors, and as seen in the table, the inductors will continue to be a limiting factor in on-chip matching networks.

A common argument to use silicon and CMOS is cost, as previously discussed, and the relative speed performance between the electron and hole carrier based devices makes silicon a preferable choice for complementary logic. To further reduce the cost, the PA can be integrated with the CMOS transceiver. While BiCMOS solves the integration of the PA and with better RF performance of the bipolar devices compared to the MOSFET devices, it has an approximately 20% higher mask count and therefore also a higher price for the same technology node [1]. Typically, GaAs have lower masks costs since less processing steps are needed, but considering yield aspects and that CMOS processes can use larger wafers, make CMOS processes favorable in mass fabrication [12]. Thus, a major benefit of using CMOS PAs is the possibility of full integration.

The historical trend of CMOS scaling has enabled high-speed CMOS devices, as seen in Table 1-1, and the trend is expected to continue, but at the expense of lower supply voltages. The supply voltage and the associated RF output power of III-V technologies are larger [12], [15]. Therefore these technologies have dominated the market of terminal PAs [25]. For higher output power, SiC, GaN, and also LDMOS have superior performance over the other devices, due to the larger supply voltage and thermal conductivity, but these technologies a lower level of integration.

Even if high-performance CMOS-based GSM/GPRS [26], GSM/EDGE [27], and WCDMA [28] PAs, as well as fully-integrated WLAN CMOS transceivers with integrated front-ends [20]-[22] have been reported, further research is needed in the field of CMOS power amplifiers. Challenges are the limitations on the supply voltage, posing challenges to meet the requirements on linearity, output power, bandwidth, and efficiency.

### 1.7 References

- [1] S. Bennett, R. Brederlow, J.C. Costa, P.E. Cottrell, W.M. Huang, A.A. Immorlica, J.-E. Mueller, M. Racanelli, H. Shichijo, C.E. Weitzel, B. Zhao, "Device and Technology Evolution for Si-Based RF Integrated Circuits," *IEEE Transactions on Electron Devices*, vol. 52, no. 7, pp. 1235-1258, July 2005.

- [2] J.S. Kilby, "Origins of the Integrated Circuit," *International Symposium on Silicon Materials Science and Technology*, vol. 98-1, pp. 342-349, 1998.

- [3] J.S. Kilby, US Patent #3,138,743, filed February 6, 1959.

- [4] R. Noyce, US Patent #2,981,877, filed July 30, 1959.

- [5] F. Wanlass, C. Sah, "Nanowatt logic using field-effect metal-oxide semiconductor triodes," *IEEE International Solid-State Circuits Conference* (*ISSCC*) *Digest*, pp. 32-33, February 1963.

- [6] G.E. Moore, "Cramming more components onto integrated circuits", *Electronics*, vol. 38, no. 8, pp. 114-117, April 1965.

- [7] G.E. Moore, "Progress in Digital Integrated Electronics", *Technical Digest of International Electron Devices Meeting*, p. 11-13, 1975.

- [8] Intel, http://www.intel.com, accessed May 2009.

1.7 References 13

[9] F. He, X. Zhou, C. Ma, J. Zhang, Z. Liu, W. Wu, X. Zhang, L. Zhang, "FinFET: From compact modeling to circuit performance," *IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC)*, pp. 1-6, December 2010.

- [10] S. Zhou, "Integration and Innovation in the Nanoelectronics Era," *IEEE International Solid-State Circuits Conference (ISSCC) Digest*, pp. 36-41, February 2005.

- [11] R. Ramzan, S. Andersson, J. Dabrowski, C. Svensson, "A 1.4V 25mW Inductorless Wideband LNA in 0.13um CMOS," *IEEE International Solid-State Circuits Conference (ISSCC) Digest*, pp. 424-425, February 2007.

- [12] F. Ellinger, *Radio Frequency Integrated Circuits and Technologies*, Berlin, Germany: Springer, Second Edition, 2008.

- [13] SKY77328 iPAC<sup>TM</sup> PAM for Quad-Band GSM/GPRS, Skyworks.

- [14] A. Raghavan, N. Srirattana, J. Laskar, *Modeling and Design Techniques for RF Power Amplifiers*, Hoboken, New Jersey, USA: John Wiley & Sons Inc., 2008.

- [15] K. Nellis, P.J. Zampardi, "A Comparison of Linear Handset Power Amplifiers in Different Bipolar Technologies," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 10, pp. 1746–1754, October 2004.

- [16] D. Su, W. McFarland, "A 2.5-V, 1-W Monolithic CMOS RF Power Amplifier," *IEEE Custom Integrated Circuits Conference (CICC) Digest*, pp. 189-192, May 1997.

- [17] K.-C. Tsai, P. Gray, "A 1.9GHz 1W CMOS Class E Power Amplifier for Wireless Communications," *IEEE European Solid-State Circuits Conference* (*ESSCIRC*), pp. 76-79, 1998.

- [18] International Technology Roadmap for Semiconductors (ITRS), 2007 Edition

Radio Frequency and Analog/Mixed-Signal Technologies for Wireless

Communications, http://www.itrs.net/, accessed May 2009.

- [19] International Technology Roadmap for Semiconductors (ITRS), 2009 Edition

Radio Frequency and Analog/Mixed-Signal Technologies for Wireless

Communications, http://www.itrs.net/, accessed May 2011.

[20] O. Degani, M. Ruberto, E. Cohen, Y. Eliat, B. Jann, F. Cossoy, N. Telzhensky, T. Maimon, G. Normatov, R. Banin, O. Ashkenazi, A. Ben Bassat, S. Zaguri, G. Hara, M. Zajac, E. Shaviv, S. Wail, A. Fridman, R. Lin, S. Gross, "A 1x2 MIMO Multi-Band CMOS Transceiver with an Integrated Front-End in 90nm CMOS for 802.11a/g/n," *IEEE Solid-State Circuits Conference (ISSCC) Digest*, pp. 356-357, February 2008.

- [21] R. Chang, D. Weber, M. Lee, D. Su, K. Vleugels, S. Wong, "A Fully Integrated RF Front-End with Independent RX/TX Matching and +20dBm Output Power for WLAN Applications," *IEEE Solid-State Circuits Conference* (*ISSCC*) *Digest*, pp. 564-565, February 2007.

- [22] S. Abdollahi-Alibeik, D. Weber, H. Dogan, W.W. Si, B. Baytekin, A. Komijani, R. Chang, B. Vakili-Amini, M. Lee, H. Gan, Y. Rajavi, H. Samavati, B. Kaczynski, S.-M. Lee, S. Limotyrakis, H. Park, P. Chen, P. Park, M. S.-W. Chen, A. Chang, Y. Oh, J. J.-M. Yang, E. C.-C. Lin, L. Nathawad, K. Onodera, M. Terrovitis, S. Mendis, K. Shi, S. Mehta, M. Zargari, D. Su, "A 65nm Dual-Band 3-Stream 802.11n MIMO WLAN SoC", *IEEE Solid-State Circuits Conference (ISSCC) Digest*, pp. 170-171, February 2011.

- [23] B.A. Floyd, C.-M. Hung, K.K. O, "The Effects of Substrate Resistivity on RF Component and Circuit Performance," *IEEE International Interconnect Technology Conference*, pp. 164-166, June 2000.

- [24] L.F Eastman, U.K. Mishra, "The toughest transistor yet," *IEEE Spectrum*, pp. 28-33, May 2002.

- [25] M.J. Franco, "Mobile handset power amplifiers," *IEEE Microwave Magazine*, vol. 10, no. 7, pp.16-19, December 2009.

- [26] I. Aoki, S. Kee, R. Magoon, R. Aparicio, F. Bohn, J. Zachan, G. Hatcher, D. McClymont, A. Hajimiri, "A Fully-Integrated Quad-Band, GSM/GPRS CMOS Power Amplifier," *IEEE Journal of Solid-State Circuits*, vol. 43, no. 12, pp. 2747-2758, December 2008.

- [27] W. Kim, K.S. Yang, J. Han, J. Chang, C.-H. Lee, "An EDGE/GSM Quad-Band CMOS Power Amplifier," *IEEE Solid-State Circuits Conference* (*ISSCC*) *Digest*, pp. 430-431, February 2011.

- [28] Black Sand Technologies, www.blacksand.com

# Chapter 2

# **CMOS Device Modeling and Parasitics**

## 2.1 Introduction

While designing digital and analog integrated circuits, it is obviously important to understand the operation of the CMOS device. The DC operation of the device is covered in [1] and not discussed in this chapter. In analog circuit design small-signal models have found widespread use as it describes the linearized operation of the transistor at a specific DC bias point. In this chapter, the small-signal model presented is based on [1], taking into account intrinsic capacitances, and also describes what extrinsic components should be included. However, notice that in PAs, the transistors are operated under large voltage swing, making the devices cross the borders between different operating regions.

## 2.2 The MOS Device

#### 2.2.1 Structure

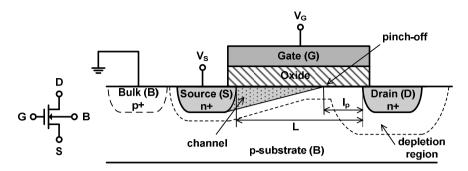

In this section the operation of an n-channel MOS (NMOS) device is considered since the main operation principles of the p-channel MOS (PMOS) device are the same. Figure 2.1 shows a simplified structure of an NMOS consisting of two strongly-doped 'n' areas in the substrate called Source (S), and Drain (D). Between the substrate and the Gate (G), there is an insulating layer made of silicon dioxide (SiO<sub>2</sub>). The device is located in a p-substrate and is called Bulk (B) or Body, typically connected to the lowest potential in the system in order to keep the source/drain junction diodes reverse-

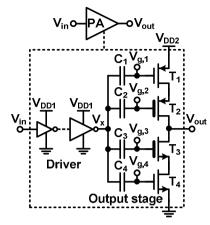

Figure 2.1: Schematic and cross section view of an NMOS transistor

biased. The region located between the drain and source, and beneath the gate, is called the channel, L, even though a channel between the drain and the source only exists under certain biasing conditions at the four terminals. Furthermore, the perpendicular extension of source and drain terminals, relatively the channel, is denoted as the width, W. The thickness of the layer separating the channel and the gate is called  $t_{ox}$  and has a physical thickness of ~1.0-5.0nm in submicron CMOS technologies.

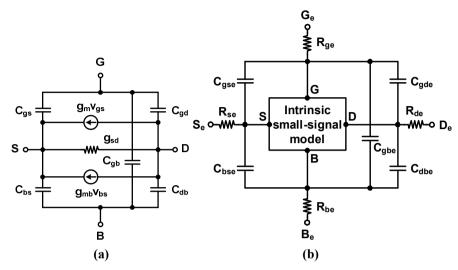

## 2.2.2 Small-Signal Model

#### 2.2.2.1 Intrinsic Model

The intrinsic small-signal model of a MOS transistor, Figure 2.2a, is obtained by independently applying small signal changes at the terminals of the device and identifying the changes in charges and currents in the device. By applying very small changes of the bias voltages at the device terminals, one at a time, and studying the effect on the drain current, an expression for the overall small change on the drain current can be expressed as in (2.1). Note that the intrinsic modeling does not include the extension of the drain and source, as well as the overlay capacitance between the gate, drain, and source shown in Figure 2.3.

In (2.1) the derivatives were replaced by a number of transconductances and the output conductance as defined in (2.2).  $g_m$  represents the gate transconductance, usually just called the transconductance.  $g_{mb}$  and  $g_{sd}$  represents the substrate transconductance and the source-drain conductance, respectively. Depending on how the transistor is biased, the transistor operates in different regions, and consequently the computation of the parameters depends on in what region the transistor operates. Assuming that the transistor operates in the saturation region, the transconductances and the source-drain conductance be computed according to (2.3)-(2.5). Combining transconductances and the intrinsic capacitances of the device a small-signal model can be drawn as in Figure 2.2a, where the output conductance is replaced by a resistor [1]. However, regarding the transconductances we can conclude that the substrate conductance,  $g_{mb}$ , only come into play as there is a difference in potential between the

2.2 The MOS Device 17

$$i_{ds} \approx g_m v_{gs} + g_{mb} v_{bs} + g_{sd} v_{ds}$$

(2.1)

$$g_{m} = \frac{\partial I_{DS}}{\partial V_{GS}}\Big|_{V_{BS}, V_{DS}}, g_{mb} = \frac{\partial I_{DS}}{\partial V_{BS}}\Big|_{V_{GS}, V_{DS}}, g_{sd} = \frac{\partial I_{DS}}{\partial V_{DS}}\Big|_{V_{GS}, V_{BS}}$$

(2.2)

$$g_m \approx \frac{2I_{DS}}{V_{GS} - V_{th}} \approx \sqrt{\frac{2\mu C_{ox}WI_{DS}}{L}}$$

(2.3)

$$g_{sd} \approx \frac{\mu C_{ox} W}{2L} (V_{GS} - V_{th})^2 \lambda \approx \lambda I_{DS}$$

(2.4)

$$g_{mb} \approx \frac{g_m \gamma}{2\sqrt{\phi_0 + V_{SR}}} \tag{2.5}$$

source and the substrate. With increasing  $V_{DS}$ , the output conductance degrades [1], leading to higher output impedance. However, further increasing  $V_{DS}$ , the depletion region associated with the drain extends further into the substrate and affects the source depletion region. Due to this interaction, the difference in potential between drain and source is lowered, resulting in lower threshold voltage. This effect is called drain-induced barrier lowering (DIBL) [2] and counteracts the impact on the output impedance, due to the channel-length modulation. Further increase of  $V_{DS}$  leads to impact ionization, lowering the output impedance [3].

These phenomenons are important in analog circuit design, as the output conductance is directly related to intrinsic voltage gain of the transistor. In a typical power amplifier circuit, the voltage swings are large (especially in the output stage), and therefore this phenomenon has an impact on the output impedance of the device. The same considerations apply to the intrinsic capacitors of the device and have to be taken into account in the transistor model in order to achieve reliable simulation results.

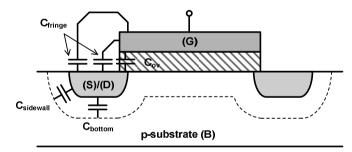

# 2.2.2.2 Extrinsic Components

Extrinsic capacitances exist between all terminals and model effects like overlay capacitances,  $C_{ov}$ , fringing capacitances,  $C_{fringe}$ , related to the extension of the drain and source,  $C_{bottom}$ , and sidewall capacitances,  $C_{sidewall}$ , as in Figure 2.3. The capacitances are added in parallel to the intrinsic small-signal model as in Figure 2.2b.

#### 2.2.3 EM-Simulated Parasitics

While there are many transistor parameters and parasitics, which can be included into the transistor model, there are also parasitics that are not directly related to the MOS device itself. If the transistor is used in power amplifier applications, the current flowing through the transistors may reach several hundred milli-amperes or even amperes. Consequently, not only the transistor has to withstand the large currents, but also the interconnections around the device. As the current flows between the drain and source, one solution is to stack several metal layers on top of each other at the drain and

Figure 2.2: (a) Intrinsic small-signal model of MOS transistor [1] (b) Small-signal model with extrinsic elements added

Figure 2.3: Extrinsic capacitances in the MOS transistor

source to meet the current density limitations of the metal traces. This would not only lead to a lower electromigration [4], but also to lower resistive voltage drop across the interconnections and introduce more capacitive coupling between gate, drain, and source as seen in Figure 2.4a. Since not all metal layers are included in the transistor model, the additional capacitances and dielectric losses need to be taken into account and added to the existing transistor model. The layout parasitics can typically be represented as either  $\pi$  or T equivalent circuits [5].

Considering the cascode amplifier stage in Figure 2.4b, used in **Paper 1** and **Paper 2**, it would have layout parasitics associated in a similar way as in Figure 2.4a. However, instead of inserting  $\pi$  or T equivalent circuits between every two nodes in the simulation model of the amplifier, the parasitic connections were approximated with series connections of capacitance and resistance between gate, drain, and source at the

2.2 The MOS Device

Figure 2.4: (a) Parasitic capacitances between gate, drain, and source (b) Model of cascode stage with parasitics, incl. the vertical gate resistance

frequency of operation. It means that two components, one resistive and one reactive component were used instead of six. The values of the parasitic components were estimated through electromagnetic simulations and depending on how the signals were applied between a pair of terminals, two different extraction formulas, based on the impedance (Z) parameters, were used. Equation (2.6) was used for differential signals and (2.7) for computation of the input impedance at port 1 [6]. In a similar way the signal traces included the series inductance and series resistance, but also the parasitic capacitance to the substrate [7]. To improve the model of the cascode stage, parasitic inductances should be included as well [8]. Considering the accuracy of the estimated parasitic impedances, the single-ended impedance has a very good accuracy since only one terminal is excited with a signal. In the differential case, when varying the amplitudes of the differential signals and the phases, the error in the simulated current between the approximate network and a  $\pi$  or T equivalent circuit representation is kept below 20%. Moreover, the parasitic impedance is placed in parallel with the small input impedance of the large devices, and the error introduced by photo-lithography effects can be as large as 20% in RC extraction from design to fabrication [9].

#### 2.2.4 Gate Resistance

To achieve a "complete" model of the device and to accurately predict power gain, input and output impedance, and phase delay between the current and the gate voltage, a number of resistive components should also be included at the drain, source, gate, and substrate. The resistive components at the drain and source typically depend on the resistivity in the regions and how the regions are contacted. Substrate resistance can be

Figure 2.5: (a) Vertical gate resistance (b) Circuit to estimate  $\omega_T$

$$Z_{dd} = Z_{11} - Z_{12} - Z_{21} + Z_{22} (2.6)$$

$$Z_{se} = Z_{11} - Z_{12}Z_{21}/Z_{22} \tag{2.7}$$

$$R_{g,lateral} = \alpha \frac{W}{L} R_{sq} \tag{2.8}$$

$$R_{g,vertical} = \frac{r_C}{WI} \tag{2.9}$$

$$C_g = C_{gs} + C_{gb} + C_{gd} (2.10)$$

$$f_T = \frac{1}{2\pi} \frac{i_o}{i_i} \bigg|_{vd=0} = \frac{1}{2\pi} \frac{g_m}{C_g} = \frac{1}{2\pi} \frac{g_m}{C_{gs} + C_{gb} + C_{gd}}$$

(2.11)

$$\omega_{\text{max}} \approx \frac{\omega_T}{\sqrt{4R'_{ge}(g_{sd} + \omega_T C_{gd})}}; R_{se} \ll R_{ge}$$

(2.12)

modeled by a single resistor up to frequencies of 10GHz [10] and as a parallel RC circuit for higher frequencies [11].

The gate has been made predominantly by silicided poly-silicon with a resistance up to  $10\Omega/\Box$  [12],  $R_{sq}$ , and the lateral gate resistance,  $R_{g,lateral}$ , can be computed according to (2.8). If the gate is connected at one side  $\alpha$  becomes 1/3, and if connected at both sides,  $\alpha$  can be reduced to 1/12 [12]. Another gate resistance component, which has not always been taken into account in the transistor models, is a contact resistance [13] between the silicide and the poly-silicon in the MOS transistor gate, denoted as  $R_{g,vertical}$  in Figure 2.5a. Assuming the contact resistivity is  $r_C$ , the additional contact resistance can be computed according to (2.9). Since the additional contact resistance may be as large as the resistance in (2.8) and is expected [13] to be the dominant factor for technologies with smaller gate lengths than 0.35µm, it is important to consider the

2.3 References 21